Про SSE я вообще не знаю где в жизни он нужен, может быть для игр? Я знаю что такое Hyper-threading (правда это не инструкция процессора, это технология), что такое VT-x, VT-d, что такое EM64T знаю, а вот что такое SSE не знаю! Ну вот такие пироги ребята

Короче ребята, я вам скажу сразу, что есть небольшой обломчик с этим делом, это я имею ввиду то, что штатными средствами винды такую штуку как SSE нельзя узнать есть она или нет. Тут нужно качать специальную прогу. Но вы не переживайте, эта супер пупер прога бесплатная, весит очень мало, комп вообще никак не грузит, но при этом она МЕГА ПОЛЕЗНАЯ и зовут ее CPU-Z (кстати скачать можно тут: cpuid.com/softwares/cpu-z.html, это официальный сайт).

Итак ребята, скачали CPU-Z, установили и потом запускаем. И вот сразу же вы все узнаете, вот сколько у меня этих SSE:

Не одна и не две, а целых шесть, огогошеньки ребята

Кстати, как видите тут еще много есть всякой полезной инфы, видите? Если срочно нужно узнать что-то о своем проце, то вы быстро запускаете CPU-Z и опа, все что вам нужно у вас под рукой! Говорю же что прога CPU-Z это одна годнота! Не верите? Ну нет проблем, я вам щас докажу. Смотрите, вот вы знаете когда у вас была выпущена та или иная планка памяти? Ну то есть дату ее выпуска на заводе так бы сказать. Или вам это не интересно? Ну некоторым очень интересно, вот мне например очень интересно! И вот прога CPU-Z может показать такую инфу! Итак ребята, смотрите, запустили CPU-Z, идете на вкладку SPD, там выбираете слот с планкой (слева), ну то есть разьем куда она установлена и смотрите инфу по выбранной планке. У меня вот стоит одна планка на 8 гигов в четвертом слоту и вот какую инфу показала прога CPU-Z:

Тут видно, что моя планка была выпущена в 30-тую неделю 2014-го года. Также написано что производитель у меня это Hyundai Electronics, ну это планка Hynix так называется

Ну короче CPU-Z это супер, если нужно быстро посмотреть вообще самую важную инфу о железе компа или ноута, она все это покажет без приколов! Короче рекомендую ребята!

И еще, забыл кое что написать про SSE. Включить или отключить SSE нельзя. Ибо эта инструкция или есть или нет. Вот например Hyper-threading включить/отключить можно, а SSE нет!

На этом все ребята, надеюсь что все вам тут было понятно, а если что-то не так, то прошу прощения. Эта инфа была вам полезной, только честно? Я буду всем сердцем надеется что да! Удачи вам в жизни, чтобы вы были здоровы и не болели, удачи

09.12.2016

Часто современный софт или игры требуют от процессора наличия инструкций SSE 4.1 — 4.2. В случае отсутствия таковых, запустить нужное приложение не получается, вылетает какая-либо ошибка или просто ничего не происходит.

FarCry 5 ругается на отсутствие SSE 4.2

При этом, мощности процессора может быть вполне достаточно для более-менее комфортной игры (к примеру, некоторый процессоры Xeon для 775 сокета до сих пор способны выдавать сносный фпс в новинках), а требование инструкций бывает необходимо даже не для самой игры, а для работы защиты от копирования. К примеру, защита Denuvo не давала владельцам старых процессоров поиграть в Assassin»s Creed Origins, хотя сама игра наличия последних инструкций не требовала.

Наличия SSE 4.1 или 4.2 требуют и другие популярные игры или их компоненты: No Man Sky, Far Cry 5, Dishonored 2, Mafia 3 и другие.

Тем не менее, решение есть, хоть и не 100% гарантирующее успех. Для запуска нужного приложения можно воспользоваться эмулятором sde external

, скачать который можно по ссылке (выбирайте версию для windows) или внизу данной статьи.

Как пользоваться эмулятором SSE 4.1-4.2

- Скачиваем архив с sde external и распаковываем так, чтобы sde.exe оказался в папке с нужной игрой или программой

- Создаем ярлык для sde.exe. Затем открываем свойства ярлыка и в параметре объект дописываем — нужный файл.exe

. Например: D:\Games\No Man»s Sky\Binaries\sde.exe» — NMS.exe. После последней кавычки должен стоять пробел, иначе система не даст сохранить ярлык. - Также в свойствах ярлыка на вкладке «Совместимость» стоит поставить опцию «запускать от имени администратора».

- Сохраняем ярлык и запускаем его. Появляется черное окно, его можно закрыть. Через некоторое время нужное приложение должно запуститься.

В новой

микроархитектуре Nehalem Intel продолжила

взятый ранее курс на увеличение числа

поддерживаемых SIMD инструкций. Пополненный

набор команд расширился за счёт семи

новых инструкций и получил название

SSE4.2 (обозначение SSE4.1 использовалось

для системы SIMD команд процессоров

Penryn). При этом Intel специально заостряет

внимание на том, что введённые в набор

SSE4.2 инструкции ориентированы не столько

на ускорение обработки потокового

медиа-контента, сколько на иные цели.

Именно поэтому новые, введённые в

Nehalem, инструкции получили также условное

обозначение ATA (Application Targeted

Accelerators).

Концепция ATA преподносится

так, что современные технологические

процессы позволяют задействовать часть

процессорных транзисторов не только

на универсальные функциональные блоки,

но и на специфические нужды, поднимая

быстродействие конкретных задач.

Так,

в соответствии с этой концепцией в

SSE4.2 добавлено пять инструкций,

предназначенных для ускорения

синтаксического анализа XML-файлов. Также

с помощью этих же инструкций возможно

увеличение скорости обработки строк и

текстов. Ещё две новые инструкции из

набора SSE4.2 нацелены на совершенно иные

приложения. Первая из них, CRC32, аккумулирует

контрольную сумму CRC32c, а вторая, POPCNT,

подсчитывает число ненулевых бит в

источнике. Эти команды также могут найти

широкое применение в различных прикладных

и сетевых приложениях.

Интегрированный контроллер памяти

Nehalem стала первой

интеловской микроархитектурой,

предполагающей интеграцию контроллера

памяти внутрь процессора. Казалось бы,

здесь инженеры Intel позаимствовали идею

своих коллег из AMD, которые встраивают

контроллер памяти внутрь процессоров

начиная с 2003 года. Однако это не совсем

так, поскольку первыми процессорами с

интегрированным контроллером памяти

должны были стать так и не вышедшие

Intel Timna, работа над которыми активно

велась в 1999 году. Кроме того, обвинения

в плагиате следует отмести и потому,

что разработанный Intel для Nehalem контроллер

памяти сильно отличается от контроллера,

эксплуатируемого в существующих

процессорах AMD. Подход Intel к проблеме

оказался куда более масштабным.

Главное

свойство контроллера памяти процессоров

семейства Nehalem – гибкость. Учитывая

модульный дизайн всего перспективного

семейства процессоров, которое может

содержать сильно различающиеся по

характеристикам и рыночному позиционированию

продукты, Intel предусмотрела возможность

не только включать или отключать

поддержку буферизированных модулей,

но и варьировать число каналов и скорость

памяти.

При этом первые процессоры с

микроархитектурой Nehalem, которые будут

выпущены в четырёхъядерном варианте,

получат трёхканальный контроллер памяти

с поддержкой DDR3 SDRAM. Таким образом,

настольные системы, построенные на

новых процессорах, смогут похвастать

непревзойдённой пропускной способностью

подсистемы памяти, которая в случае

использования трёх модулей DDR3-1067

достигнет 25,6 Гбайт/с.

Впрочем, основное

преимущество переноса контроллера DRAM

в процессор заключается не столько в

росте пропускной способности, сколько

в уменьшении латентности подсистемы

памяти. Несмотря на то, что Intel предлагает

использовать с новыми процессорами

DDR3 память, отличающуюся относительно

высокой латентностью, задержки при

обращении Nehalem к памяти будут в любом

случае ниже, чем в системах, основанных

на процессорах Core 2 и использующих DDR3

SDRAM (и, наверняка, DDR2 SDRAM).

Для подтверждения

этих слов хотелось бы привести данные,

полученные при измерении практических

параметров подсистемы памяти системы

на базе Nehalem в тестовой утилите Everest

4.60.

Таблица

2. Тестирование работы памяти

Собственно,

даже работая в одноканальном режиме,

контроллер памяти Nehalem способен показать

лучшую производительность, чем контроллер

памяти сегодняшних LGA775 платформ. Это

совершенно закономерный результат, так

как на пути между процессором и памятью

в системах нового поколения нет никаких

промежуточных устройств – в то время

как ранее за работу с памятью отвечал

северный мост чипсета, который вносил

собственные весьма существенные

задержки, вызванные необходимостью

синхронизации шин памяти и FSB.

Ещё

одно косвенное преимущество встроенного

в процессор памяти заключается в том,

что его функционирование теперь не

зависит ни от чипсета, ни от материнской

платы. В результате, Nehalem будет показывать

одинаковую скорость работы с памятью

при работе в платформах различных

разработчиков и производителей.

Время на прочтение

8 мин

Количество просмотров 12K

Можно ли добавить в микропроцессор инструкции (команды)? Если вы используете микросхемы ПЛИС / FPGA с реконфигурируемой логикой и микропроцессорное ядро, которые синтезирутся из описания на языках Verilog и VHDL, то можете. Причем это будет «честное», настоящее расширение системы команд, а не трюк типа программной эмуляции инструкции в обработчике исключения от зарезервированной команды, и не «микрокод», популярный в исторических процессорах 1970-х годов.

Команды, добавленные в современный синтезируемый процессор с помощью модификации его исходников на Verilog или VHDL, могут работать в конвейере и обрабатываться процессором как его собственные, без временных задержек.

Главная проблема с модификацией исходников дизайна процессора на Verilog или VHDL — трудоемкость. Нужно понять, как работает логика различных блоков и избежать нежелательных побочных эффектов. К счастью, существует способ расширения процессора, который превращает семестровый студенческий проект в нечто, что студент может спроектировать за одну лабораторную работу. Этот способ — интерфейс CorExtend / UDI (User Defined Instructions) в микропроцессорном ядре MIPS microAptiv UP, которое используется в пакете для образования MIPSfpga.

В рамках университетской программы MIPSfpga компании Imagination Technologies можно скачать настоящий индустриальный код на Verilog процессора MIPS microAptiv UP.

https://community.imgtec.com/university/resources/

Одним из распространенных применений UDI является манипуляции битами в алгоритмах шифрования. Другой пример — создание специальных инструкций для ускорения алгоритмов ЦОС Accelerating DSP Filter Loops with MIPS® CorExtend® Instructions.

Однако в наборе документации к MIPSfpga интерфейс между ядром и CorExtend описан недостаточно подробно. Подробная документация предоставляется только лицензиатам ядер. В этой статье представлено мое описание данного интерфейса на основе изучения исходного кода. Его можно также скачать в формате pdf MIPS microAptiv UP Processor CorExtend UDI interface protocol guide.

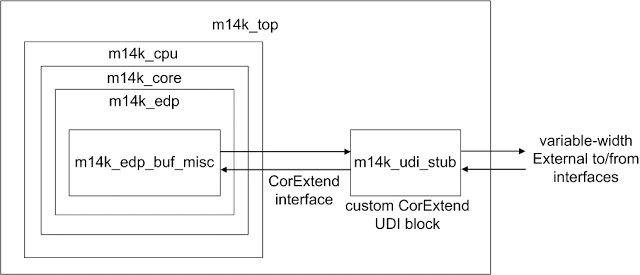

CorExtend занимает следующее место в RTL иерархии ядра m14k microAptiv.

Все сигналы уровня m14k_cpu, включая CorExtend UDI, описаны в документе MIPS32 microAptiv UP Processor Core Family Integrators Guide (Таблица 2.3 Signal Descriptions for m14k cpu Level). Лучше смотреть там, но для наглядности ниже приведена выдержка оттуда исключительно с сигналами CorExtend UDI.

| Название сигнала | Тип | Описание |

| UDI_ir_e[31:0] | Out | Полное слово инструкции. Хотя модуль получает rs и rt операнды, передается инструкция целиком, чтобы была возможность передавать данные в полях адресов операндов. Обратите внимание, что тот, кто будет реализовывать собственный UDI блок, должен самостоятельно декодировать поля Opcode и Function field. |

| UDI_irvalid_e | Out | Сигнал valid для слова инструкции (UDI_ir_e). |

| UDI_rs_e[31:0] | Out | Операнд rs. |

| UDI_rt_e[31:0] | Out | Операнд rt. |

| UDI_endianb_e | Out | Сигнализирует, что инструкция исполняется в режиме Big Endian. Сигнал обычно не нужен, кроме случаев, когда a) инструкция UDI оперирует с частью слова данных и зависима от endian, b) UDI блок работает в режиме big-endian. |

| UDI_kd_mode e | Out | Сигнализирует, что инструкция исполняется в kernel или debug режиме. Может быть использовано для предотвращения исполнения некоторых инструкций в kernel или debug режимах. |

| UDI_kill_m | Out | Сигнал kill от исключения, сгенерированного предыдущей инструкцией. Может быть использован для снятия UDI_stall_m, что уменьшит задержку у многотактовых UDI инструкций, чьи результаты не будут использоваться. |

| UDI_start_e | Out | Сигнал mpc_run_ie из блока управления (Master Pipeline Control). |

| UDI_run_m | Out | Сигнал mpc_run_m, использующийся как valid для UDI_kill_m. |

| UDI_greset | Out | Reset, может быть использован для сброса автоматов в UDI блоке. |

| UDI_gclk | Out | Clock input в UDI блоке. |

| UDI gscanenable | Out | Global scan enable. |

| UDI_ri_e | In | Сигнализирует Master Pipeline Control (MPC) о том, что исполняемая в данный момент инструкция зарезервирована. Однако MPC примет его во внимание, только если инструкция входит в подмножество user-defined инструкций SPECIAL2 (биты [5:4] в инструкции 2’b01). |

| UDI_rd_m[31:0] | In | 32-битный результат выполненной инструкции, доступный на стадии M (Memory fetch). |

| UDI_wrreg_e[4:0] | In | Адрес регистра для записи результата выполнения user-defined инструкции. Также передается в MPC. |

| UDI_stall_m | In | Сигнализирует, что UDI блок выполняет многотактовую инструкцию и должен остановить конвейер перед записью в регистр общего назначения. должен быть установлен в 0 для однотактовых инструкций. Сигнал стадии M. |

| UDI_present | In | Статический сигнал, означающий что UDI блок доступен. |

| UDI_honor_cee | In | Показывает, должен ли процессор принимать во внимание CorExtend Enable (CEE) бит Status регистра. Если UDI_honor_cee установлен в единицу и Status.CEE бит Status регистра не установлен, сгенерируется исключение CorExtend Unusable Exception. |

Кроме этих сигналов у CorExtend блока есть внешние сигналы с количеством бит, определяемым разработчиком.

| Название сигнала | Тип | Описание |

| UDI_toudi[x-1:0] | In | Внешний вход CorExtend блока переменной длины. |

| UDI_fromudi[x-1:0] | Out | Внешний выход CorExtend блока переменной длины. |

Чтобы создать свой CorExtend блок необходимо изменить файлы m14k_edp_buf misc и m14k_udi_stub should. В файле

m14k_edp_buf_misc входные и выходные порты можно соединить, например, вот так.

assign UDI_ir_e[31:0] = mpc_ir_e ;

assign UDI_irvalid_e = mpc_irval_e ;

assign UDI_rs_e[31:0] = edp_abus_e ;

assign UDI_rt_e[31:0] = edp_bbus_e ;

assign UDI_endianb_e = cpz_rbigend_e ;

assign UDI_kd_mode_e = cpz_kuc_e ;

assign UDI_kill_m = mpc_killmd_m ;

assign UDI_start_e = mpc_run_ie ;

assign UDI_run_m = mpc_run_m ;

assign UDI_greset = greset ;

assign UDI_gscanenable = gscanenable ;

assign UDI_gclk = gclk ;

assign edp_udi_wrreg_e[4:0] = UDI_wrreg_e ;

assign edp_udi_ri_e = UDI_ri_e ;

assign edp_udi_stall_m = UDI_stall_m ;

assign edp_udi_present = UDI_present ;

assign edp_udi_honor_cee = UDI_honor_cee ;

mvp_mux2 #(32) _res_m_31_0_(res_m[31:0],mpc_udislt_sel_m, asp_m, UDI_rd_m);

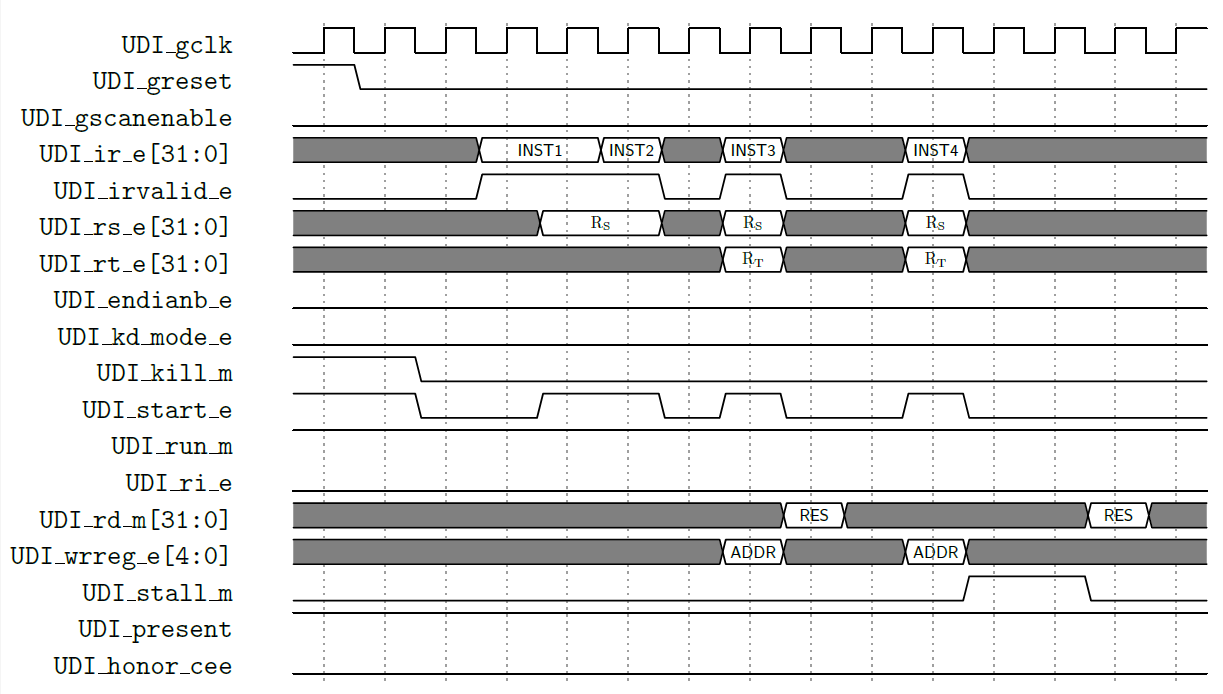

Сам CorExtend блок должен заменить файл m14k_udi_stub. Пример взаимодействия между CorExtend и ядром microAptiv UP представлена на временной диаграмме ниже.

Сигнал UDI_present должен быть подтянут к единице. UDI_honor_cee может быть подтянут к нулю. Если его подтянуть к единице, то прежде чем выполнять инструкции CorExtend необходимо будет взвести бит Status CEE инструкцией mtc0. Если этого не сделать, появится исключение CorExtend unusable exception и на следующем такте после UDI_start_e выставится сигнал UDI_kill_m на два такта.

Частично инструкция должна быть декодирована на том же такте, на котором появился сигнал UDI_start_e. Это необходимо для формирования сигнала UDI_ri_e, который следует выставлять одновременно с появлением UDI_start_e в случае если инструкция зарезервирована. Если инструкция подразумевает запись результата в регистр общего назначения, его адрес также должен быть выставлен на UDI_wrreg_e[4:0] одновременно с UDI_start_e. Остальные поля инструкции можно записать в регистр и декодировать позднее.

Сигнал UDI_wrreg_e[4:0] может адресовать 31 регистр общего назначения, значение 5’d0 означает отсутствие записи в регистры.

Результат UDI инструкции, который должен быть записан в регистр общего назначения должен выставляться на UDI_rd_m[31:0] на следующем такте после UDI_start_e. Если он должен быть записан позднее, на следующем такте после UDI_start_e следует выставить UDI_stall_m. UDI_stall_m следует сбросить в ноль за один такт перед выставлением результата на UDI_rd_m[31:0].

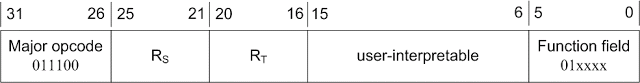

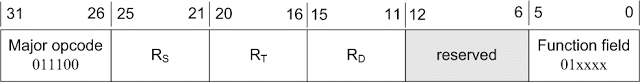

На рисунке ниже представлен общий формат инструкции UDI. Поле Major opcode входит в подмножество special2 и равно 6’d28. Поля RS и RT содержат адреса регистров операндов. Биты 15..6 могут быть использованы по усмотрению разработчика. Например, туда можно записать адрес регистра назначения для записи результата или передать мгновенное значение. Поле Function field состоит из бит 5..4, которые всегда равны 2’b01, и бит 3..0, с помощью которых можно закодировать до 16 UDI инструкций.

Разработка CorExtend блока проиллюстрирована следующим примером DSP ускорителя, который рассчитывает мгновенную мощность комплексного сигнала, который определен, как

P(t) = a2(t) + b2(t),

где a(t) и b(t) — действительная и мнимая части сигнала соответственно.

Эта операция полезна для детектирования сигнала путем его сравнения с пороговым значением.

В таблице ниже приведены инструкции DSP ускорителя.

| Инструкция | Описание | function field |

| UDI0 RD; RS; RT | RD = RS[31:16]2 + RT[31:16]2 | 6’b010000 |

| UDI1 RD; RS; RT | RD = (RS[31:16]2 + RT[31:16]2) >> 1 | 6’b010001 |

| UDI2 RD; RS | RD = RS[31:16]2 | 6’b010010 |

| UDI3 RS | stored_threshold = RS | 6’b010011 |

| UDI4 RD; RS; RT | RD = ( (RS[31:16]2 + RT[31:16]2) > stored_threshold )? 1:0 | 6’b010100 |

| UDI5 RD; RS; RT | RD = ( ((RS[31:16]2 + RT[31:16]2) >> 1) > stored_threshold )? 1:0 | 6’b010101 |

| UDI6 RD; RS; RT | RD = ( RS[31:16]2 > stored_threshold )? 1:0 | 6’b010110 |

UDI0 вычисляет мгновенную мощность сигнала. Операнды RS и RT содержат 16-битные действительные и мнимые части сигнала. 32-битный результат записывается в регистр общего назначения по адресу RD.

UDI1 делает то же, что и UDI0. Различие в том, что UDI1 сдвигает результат для предотвращения переполнения.

UDI2 вычисляет мгновенную мощность сигнала, используя только действительную часть сигнала. RT операнд не используется.

UDI3 записывает 32-битное пороговое значение во внутренний регистр блока CorExtend, результат не возвращается.

UDI4, UDI5 и UDI6 выполняют операции инструкций UDI0, UDI1 и UDI2 соответственно и сравнивают результат с сохраненным пороговым значением. Если порог превышен, возвращается результат 32’d1, иначе 32’d0.

Все инструкции, кроме UDI3, пишут результаты в регистры общего назначения, для чего необходимо указать его адрес. Для этого было введено поле RD, как показано на рисунке ниже.

Код ниже показывает пример программы на языке MIPS ассемблера для тестирования всех разработанных UDI инструкций.

Machine Code Instruction Address Assembly Code

3c088000 // bfc00000: lui $8, 0x8000

3c09beaf // bfc00004: lui $9, 0xbeaf

71095010 // bfc00008: udi0 $8 $9 $10

71095011 // bfc0000c: udi1 $8 $9 $10

71005012 // bfc00010: udi2 $8 $10

3c0bbeaf // bfc00014: lui $11, 0xbeaf

356bdead // bfc00018: ori $11,$11, 0xdead

71600013 // bfc0001c: udi3 $11

71095014 // bfc00020: L1: udi4 $8 $9 $10

71095015 // bfc00024: udi5 $8 $9 $10

71095016 // bfc00028: udi6 $8 $9 $10

3c0b0001 // bfc0002c: lui $11, 0x0001

356bfeed // bfc00030: ori $11,$11, 0xfeed

71600013 // bfc00034: udi3 $11

1000fff9 // bfc00038: beq $0, $0, L1

00000000 // bfc0003c: nop

Пример проекта с реализацией блока CorExtend с вышеперечисленными инструкциями можно скачать по ссылке https://github.com/zatslogic/UDI_example.

Проект включает в себя исходный код для симуляции за исключением файлов из директории rtl_up. Чтобы их получить необходимо зарегистрироваться в Imagination University Programme и с делать запрос на загрузку (https://community.imgtec.com/downloads/mipsfpga-getting-started-version-1-2). Также для запуска симуляции необходимо иметь XilinxCorelib, его можно скомпилировать в Vivado командой compile_simlib.

Проект включает в себя два варианта реализации CorExtend блока. В первом случае все инструкции UDI выполняются за один такт. Во втором были вставлены дополнительные регистры и некоторые инструкции требуют больше тактов для исполнения. Это было сделано специально, чтобы задействовать сигнал UDI_stall_m.

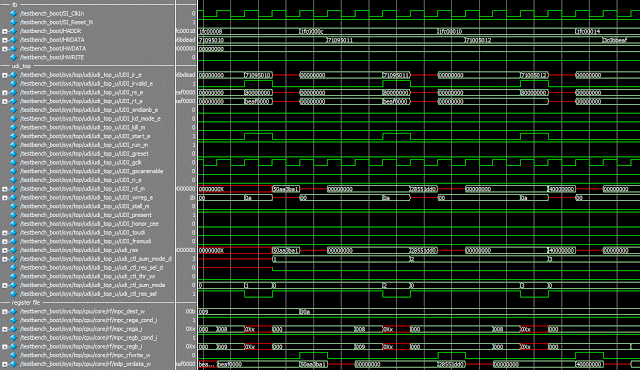

На временных диаграммах далее представлена симуляция приведенной выше программы на ассемблере.

Для первого однотактного варианта блока инструкции UDI0, UDI1 и UDI2 выполняются следующим образом.

Можно видеть, что инструкции появляются на UDI_ir_e с сигналами UDI_irvalid_e и UDI_start_e. Операнды также доступны на этом такте. На этом же такте формируется адрес записи результата в регистр общего назначения. Результат выставляется на UDI_rd_m на следующем такте.

Кроме того, на временной диаграмме представлены сигналы блока регистров общего назначения. Адрес записи в них может быть виден на mpc_dest_w. Данные представлены на edp_wrdata_w с сигналом write enable на mpc_rfwrite_w. Сигналы mpc_rega_i и mpc_regb_i содержат адреса операндов, считываемых из регистров общего назначения.

На данной временной диаграмме показано выполнение инструкций UDI3, UDI4, UDI5 и UDI6.

Как видно из листинга программы на ассемблере UDI3 записывает 0xbeafdead в stored_threshold. Результаты выполнения инструкций UDI4, UDI5 и UDI6 — нули, т.к порог ни разу не был превышен.

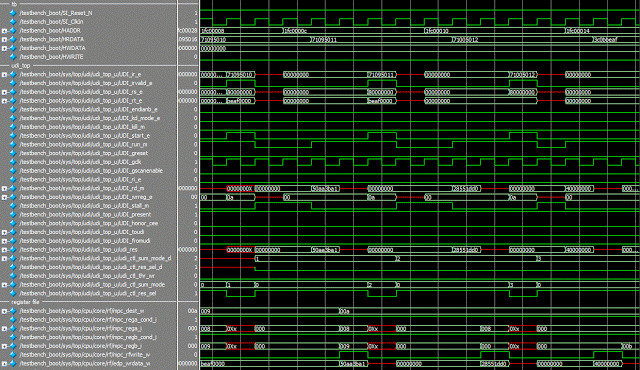

На следующей временной диаграмме выполняются инструкции UDI3, UDI4, UDI5 и UDI6 после условного перехода. Теперь пороговое значение меньше результатов вычислений и можно видеть, что в регистры результатов пишется 0x000001.

Следующие три временные диаграммы показывают симуляцию блока UDI с дополнительными регистрами.

На данной временной диаграмме видно исполнение инструкций UDI0, UDI1 и UDI2. На время выполнения вычислений выставляется сигнал UDI_stall_m. На следующий такт после его снятия выставляется результат на UDI_rd_m. Еще через такт результат записывается в регистры общего назначения.

На данной временной диаграмме представлены инструкции UDI4, UDI5 и UDI6 с сигналом UDI_stall_m.

На после ней временно диаграмме выполняются инструкции UDI4, UDI5 и UDI6 после условного перехода.

Надеюсь, данный материал окажется полезным для тех, кто захочет также поучаствовать в программе MIPSfpga и создать проект с использованием UDI инструкций.

Всем привет. На моем процессоре Xeon X5670 нет AVX инструкций, которые на данный момент требуются в играх Journey и Flower (один и тот же разработчик), но я хочу в них поиграть, а процессор менять не собираюсь. Недавно нашел комментарий в Steam-обществе steamcommunity. com/app/966330/discussions/0/3247562523070871218/ (уберите лишний пробел в адресе), согласно которому существует возможность запуска игр (с отладкой приложения), требующих AVX на ПК, которые такими инструкциями не обладают. Для этого нужен компонент «intel sde (Software Development Emulator)» для эмуляции AVX-инструкций. Он устанавливается поверх Microsoft Visual Studio 2012-2015 (более поздние версии возможно тоже поддерживаются).

Что получилось сделать у себя из задуманного:

1. Установил Visual Studio 2012

— снять галочки со всех компонентов кроме «Microsoft Foundation Classes для C++»

2. Установил пакет sde-msvs2015-3.0.2 (intel sde)

На чем остановился (дальше не знаю что делать):

3. По идее нужно открыть Visual Studio 2012 и в меню «Файл»-«Открыть»-«Решение или проект»-«Исполняемые файлы проектов» указать на запускной (.ехе) файл игры, после чего в меню «Отладка» нажать «Начать Отладку».

— У меня на данном этапе, после нажатия на кнопку «Начать Отладку» выскакивает куча ошибок (игра не запускается), первая из которых эта (пробовал с игрой Flower):

— Возможно следует запускать игру через с параметром «sde —«, как указано ниже из примера использования Intel SDE (как запустить игру с ним не знаю, пробовал дописать как аргумент в свойствах запуска файла внутри Visual Studio — не помогает).

Информация, которая поможет разобраться как работает эмуляция AVX в Visual Studio, описана на русском здесь: habr. com/ru/post/99367/ (уберите лишний пробел в адресе)

Я выделили для себя наиболее важные положения оттуда:

Чтобы убедиться в работоспособности AVX кода лучше написать к нему Unit-тесты. Однако встаёт вопрос: как запустить эти Unit-тесты, если ни один ныне продаваемый процессор не поддерживает AVX? В этом вам поможет специальная утилита от Intel — Software Development Emulator (SDE). Всё, что умеет SDE — это запускать программы, на лету эмулируя новые наборы инструкций. Разумеется, производительность при этом будет далека от таковой на реальном железе, но проверить корректность работы программы таким образом можно. Использовать SDE проще простого: если у вас есть unit-тест для AVX кода в файле avx-unit-test.exe и его нужно запускать с параметром «Hello, AVX!», то вам просто нужно запустить SDE с параметрами

sde — avx-unit-test.exe «Hello, AVX!»

При запуске программы SDE сэмулирует не только AVX инструкции, но также и инструкции XGETBV и CPUID, так что если вы используете предложенный ранее метод для детектирования поддержки AVX, запущенная под SDE программа решит, что AVX действительно поддерживается. Кроме AVX, SDE (вернее, JIT-компилятор pin, на котором SDE построен) умеет эмулировать SSE3, SSSE3, SSE4.1, SSE4.2, SSE4a, AES-NI, XSAVE, POPCNT и PCLMULQDQ инструкции, так что даже очень старый процессор не помешает вам разрабатывать софт под новые наборы инструкций.

Использование AVX в коде на C/C++

Поддержка AVX реализована в следующих популярных компиляторах:

— Microsoft C/C++ Compiler начиная с версии 16 (входит в Visual Studio 2010)

— Intel C++ Compiler начиная с версии 11.1

— GCC начиная с версии 4.4

Помню ещё в 90-е была программка которая CD привод для чтения добавляла режим записи. Может она уже и в процессоры умеет.

anonymous

()

- Показать ответы

- Ссылка

Не вижу вопроса, что сказать то хотел.

anonymous

()

- Ссылка

Ответ на:

комментарий

от anonymous

Это была не программка а прошивка для CD привода. Ряд производителей для унификации и экономии выпускали одинаковые пишущие CD приводы но одни с прошивкой разрешающей только чтение а другие с прошивкой разрешающей и чтение и запись. Такие приводы можно было научить писать всего лишь сменой прошивки

anonymous

()

- Ссылка

Чё только кукурузники не удумают.

anonymous

()

- Ссылка

qemu-user

anonymous

()

- Ссылка

Такой вопрос: можно ли их как то добавить в процессор, если например модифицировать microcode.

Вы это серьёзно? Конечно современная наука и производство «временами/местами» на грани фантастики, но чтобы можно было добавить «прошивкой»(микрокодом) новый набор инструкций… Или я пропустил «революцию в создании CPU»?

anymouze ★★

()

- Показать ответ

- Ссылка

Может ты еще хочешь модифицировать микрокод, чтобы свою кукурузу в рязань превратить? А, тролль четырехзвездный?

anonymous

()

- Ссылка

Добавить поддержку SSE4 при помощи специального микрокода — теоретически возможно, но ты столкнёшься со следующими трудностями: 1) размер микрокода ограничен и зависит от конкретного процессора. могу ошибаться (т.к. ты не сказал конкретный CPU ID), но если CPU ID твоего Phenom X4 — 0x100F41 — то размер твоего микрокода 960 байт = 0x3C0 2) сам микрокод, его структура и формат — проприетарны, поэтому ты не сможешь сам написать микрокод дающий поддержку SSE4. Но если тебе удастся найти похожий процессор с тем же размером микрокода и похожей архитектурой, но поддерживающий SSE4, ты можешь попытаться подгрузить его микрокод на свой процессор в надежде что SSE4 появится. Или модификацией твоего проприетарного UEFI/BIOS (у тебя же не опенсорсный coreboot/SeaBIOS) что более надёжно, или правкой таблиц эквивалентности в файле microcode_amd.bin из используемого твоим дистрибутивом amd-ucode. Подробнее о формате этого контейнера — например здесь: https://github.com/coreboot/coreboot/blob/4f16049f17a4dcbf329d6b30f0d00f0a7f5… но вместо

* [8-11] Size (n) in bytes of variable portion of container header

* [12-n] don’t-care

там

* [12-(12+n)] таблица эквивалентности

вида

CPU_ID процессора — 8 нулей — ID в заголовке микрокода

CPU_ID процессора — 8 нулей — ID в заголовке микрокода

…

последние 16 нулей как завершение (они тоже учитываются в составе числа n, таким образом минимально возможный размер таблицы эквивалентности: одна строка 0x10 + шестнадцать нулей 0x10 = 0x20)

если CPU_ID процессора соответствует ID в заголовке микрокода, то этот микрокод будет подгружен на этот процессор. соответственно, подменив CPU_ID в определённом месте на свой, можно заставить подгрузить конкретный микрокод на свой процессор. главное не забыть в другом месте удалить уже свой CPU_ID, т.к. одному CPU_ID должен соответствовать один микрокод. то есть лучше будет просто поменять местами два CPU ID

Ещё вариант, пытаться делать это не через микрокод а через другие способы разблокировки. Как там 4 ядро у некоторых процессоров АМД разблокировали? Ещё есть AMD HDT Debug connector, на некоторых матплатах даже распаянный, к нему можно подключить отладчик и пытаться разблокировать нужные тебе фичи если они там в железе есть но тупо выключены по каким-то причинам (как например в некоторых пеньках 4 под сокет 478 в железе процессора была поддержка 64-бит но искусственно выключена) Поищи в интернете AMD HDT Debug / Debugger, для начала можно немного почитать можно здесь — https://www.theregister.co.uk/2010/11/15/amd_secret_debugger/ и здесь — https://forums.overclockers.ru/viewtopic.php?t=144934

SakuraKun ★★★★★

()

- Показать ответ

- Ссылка

Ответ на:

комментарий

от SakuraKun

Ну ты и аут, столлько настрочить в ответ на такую тупость.

anonymous

()

- Ссылка

проще программу пропатчить

xmikex ★★★★

()

- Ссылка

Ответ на:

комментарий

от anymouze

Intel недавно добавляла новые инструкции для закрытия дыр.

anonymous

()

- Показать ответы

- Ссылка

Ответ на:

комментарий

от i-rinat

Мне вот интересно, если эмуляция FPU в ядре есть, можно ли такое же прикрутить для SSE и сотоварищи? Чисто с теоретической точки зрения…

- Показать ответы

- Ссылка

Ответ на:

комментарий

от timdorohin

Я как-то ради интереса заводил подобное обсуждение тут на ЛОРе.

Решили, что оверхед будет наглухо убивать все плюсы эмуляции наборов инструкций.

devl547 ★★★★★

()

- Показать ответ

- Ссылка

Ответ на:

комментарий

от devl547

FPU тоже эмулировали не ради производительности, а ради совместимости. Особенно если в дело вступают блобы…

- Ссылка

Ответ на:

комментарий

от anonymous

про исправление ошибок/«дыр» микрокодом знаю. про добавление инструкции (1-й), а тем более набора команд никогда не слышал.

anymouze ★★

()

- Показать ответы

- Ссылка

Попробуй зубилом, молотком и паяльником. И киянкой в конце нежно-нежно пройтись.

targitaj ★★★★★

()

- Ссылка

Ответ на:

комментарий

от timdorohin

можно ли такое же прикрутить для SSE и сотоварищи? Чисто с теоретической точки зрения…

Можно. Но проще будет такое в юзерспейсе сделать.

Цепляешься к процессу, как gdb цепляется, ловишь SIGILL и эмулируешь инструкции, которые процессор не осилил.

i-rinat ★★★★★

()

Последнее исправление: i-rinat

(всего

исправлений: 1)

- Ссылка

Ответ на:

комментарий

от anymouze

Что сказать-то хотел? Что новости не читаешь?

anonymous

()

- Показать ответ

- Ссылка

Ответ на:

комментарий

от anonymous

Он скор набивает, кто-то из недавно забаненых.

anonymous

()

- Ссылка

Кроме шуток, я слышал, что под винду, например, есть специальные отладочные средства, которые не лету патчат код работающей программы и заменяют не поддерживаемые инструкции и заменяют их программной эмуляцией. Конечно, это все жутко тормозит, но все же кое-как работает.

Хотелось бы узнать, есть ли аналоги под линукс.

Khnazile ★★★★★

()

- Показать ответы

- Ссылка

я за бан.

Deleted

()

- Ссылка

Ответ на:

комментарий

от Khnazile

Ответ на:

комментарий

от Khnazile

Кроме шуток, я слышал, что под винду, например, есть специальные отладочные средства, которые не лету патчат код работающей программы и заменяют не поддерживаемые инструкции и заменяют их программной эмуляцией. Конечно, это все жутко тормозит, но все же кое-как работает.

Если программа не модифицирует свой код на лету и не проверяет контрольную сумму кода, тогда что мешает на участках с не поддерживаемыми инструкциями сделать jmp(это если аналогичные инструкции не влезут в тот-же размер) на аналог с поддерживаемыми инструкциями? Ни каких жутких тормозов в таком случае быть не должно.

V1KT0P ★★

()

- Показать ответ

- Ссылка

Такой вопрос: имеем этот процессор.

Решил я попробовать vpp от fd.io, но он мне пишет, что мой cpu не поддерживает данный набор инструкций.

Такой вопрос: можно ли их как то добавить в процессор, если например модифицировать microcode.

Ты этот VPP имеешь ввиду: https://github.com/FDio/vpp ?

Это после сборки он тебе такое говорит или ты бинарь готовый качал?

V1KT0P ★★

()

- Показать ответ

- Ссылка

Ответ на:

комментарий

от V1KT0P

тогда что мешает

Статическая рекомпиляция — сложная штука. Каждая мелочь может превратить казалось бы простую задачу в нерешаемую.

i-rinat ★★★★★

()

- Показать ответ

- Ссылка

Ответ на:

комментарий

от V1KT0P

Ответ на:

комментарий

от Khnazile

Ответ на:

комментарий

от i-rinat

Интересная штука, спасибо. Не думаю, что лично мне это будет когда-нибудь полезно, но все же хорошо знать, что такое есть.

Khnazile ★★★★★

()

- Ссылка

Суровые линуксоиды не только пишут программы, но и добавляют инструкции в процессор самостоятельно!

А что сделал я ради линукса?

Deleted

()

- Показать ответ

- Ссылка

Ответ на:

комментарий

от Deleted

да молодец! купил себе целый новый комп ради линукса!

sqq ★

()

- Ссылка

Ответ на:

комментарий

от i-rinat

Статическая рекомпиляция — сложная штука. Каждая мелочь может превратить казалось бы простую задачу в нерешаемую.

Если там нет защиты и еще чего-то хитрого, то все просто. Вон под оффтопик на cheatengine патчат игры и ничего работает, даже я на лету для пары игр код патчил, а ведь это именно изменение поведения кода а не замена его на аналогичный код просто другими инструкциями.

V1KT0P ★★

()

- Показать ответ

- Ссылка

Ответ на:

комментарий

от V1KT0P

Ответ на:

комментарий

от ne-vlezay

Ответ на:

комментарий

от anymouze

про добавление инструкции (1-й), а тем более набора команд никогда не слышал.

Transmeta так делала)

devl547 ★★★★★

()

- Показать ответы

- Ссылка

Ответ на:

комментарий

от i-rinat

Ты пробовал реализовывать нечто подобное?

Нет, но вот беглое гугление показывает статью https://habr.com/post/310864/ где замена popcnt из SSE4.2 для AMD драйвера позволила использовавть DirectX12. Не вижу в этом ничего страшного и сложного, проблема будет разве что с ПО на котором висит протектор какой или подсчет контрольной суммы(хотя и это можно пофиксить).

А вот эпичное портирование бинаря Starcraft с x86 на ARM: https://habr.com/post/215375/

Главное это желание =).

V1KT0P ★★

()

- Показать ответ

- Ссылка

Ответ на:

комментарий

от V1KT0P

Ответ на:

комментарий

от anonymous

20 лет

SSE4 был анонсирован 27 сентября 2006 года

<zanuda>Эээ… Я не смог округлить 12 до 20, извини конечно. Но 12 лет — тоже ничего так срок, тут вопросов нет.</zanuda>

Pinkbyte ★★★★★

()

- Показать ответ

- Ссылка

Ответ на:

комментарий

от Pinkbyte

SSE4 был анонсирован 27 сентября 2006 года

SSE4.2 появился в 2008, так что 10 лет. У AMD — в 2011.

i-rinat ★★★★★

()

- Показать ответ

- Ссылка

Ответ на:

комментарий

от devl547

За подсказку спасибо!одну или набор?<ушёл в поиск>

anymouze ★★

()

- Ссылка

Ответ на:

комментарий

от anonymous

давно пора, почти 20 лет прошло всё-таки

Phenom X4 — 2008 год, всего лишь 10 лет назад.

Phenom II/Athlon II — 2011 год, всего 7 лет назад.

Неплохие процессоры, зачем принудительно ограничивать если сборка без SSE4 уже и так была?

V1KT0P ★★

()

- Показать ответы

- Ссылка

Ответ на:

комментарий

от i-rinat

Спасибо за поправку. Тем более анонимус не прав — тут даже если сильно тянуть за уши — не округляется

Pinkbyte ★★★★★

()

- Показать ответ

- Ссылка

Ответ на:

комментарий

от V1KT0P

беглое гугление показывает статью https://habr.com/post/310864/ где замена popcnt из SSE4.2 для AMD драйвера позволила использовавть DirectX12

Это ручная работа. И повезло, что там было место рядом, в которое можно прыгнуть относительным джампом.

А вот эпичное портирование бинаря Starcraft с x86 на ARM

Вот и я на него намекал. Я аналогичным образом конвертировал Android-версию Opera Mini с ARM на MIPS. И там были сложности. Вроде всё просто ноначалу. А потом: бац, бац, бац, бац-бац-бац, бац, бац… «Ну, а что вы хотели?»

i-rinat ★★★★★

()

- Показать ответ

- Ссылка

Ответ на:

комментарий

от Pinkbyte

Смотри, если взять 20 за единицу, то 10 уже округляется до 20.

anonymous

()

- Показать ответ

- Ссылка

Ответ на:

комментарий

от anonymous

Ответ на:

комментарий

от Pinkbyte

Моя версия — 12 и 20 это тренарная запись, тогда инкремент на единицу 12 приведет к 20.

Aber ★★★★★

()

- Показать ответ

- Ссылка

Ответ на:

комментарий

от V1KT0P

Амд изначально ничего не хотела поддерживать, она хотела свои уникальные проприетарные симд, чтобы софт лучше работал только у неё. Что-то пошло не так. Сейчас предпринимает новые попытки завязать пользователей на себя. Других способов конкурировать то нет.

anonymous

()

- Показать ответы

- Ссылка

Ответ на:

комментарий

от Aber

Блин, шо ж вы оффтопить провоцируете, демоны?! Тем не менее всё равно нет, хотя эту за эту попытку зачет

Pinkbyte ★★★★★

()

- Ссылка

Вы не можете добавлять комментарии в эту тему. Тема перемещена в архив.

Микрокод процессора — это набор инструкций, записанных во встроенной памяти самого процессора. Он определяет основные функции и операции, которые может выполнять процессор. В ходе использования может возникнуть необходимость обновить или дополнить микрокод, чтобы улучшить работу процессора или исправить обнаруженные ошибки.

Но как добавить микрокод процессора в BIOS? Для этого вам понадобится биос-обновление – процесс обновления программного обеспечения BIOS, включающий в себя замену или добавление микрокода процессора. Это важная процедура, которая может улучшить производительность вашего компьютера и обеспечить его стабильную работу.

Прежде чем приступить к обновлению BIOS, нужно убедиться, что вы имеете последнюю версию прошивки BIOS для вашего материнской платы. Обычно такие обновления можно найти на официальном сайте производителя материнской платы или на сайте производителя компьютера или ноутбука.

Однако перед обновлением BIOS обязательно прочтите инструкции, приложенные к обновлению. Убедитесь, что вы делаете все правильно, чтобы избежать проблем и потери данных. Следуйте пошаговой инструкции, которая обычно прилагается вместе с обновлением BIOS. Не закрывайте компьютер и не отключайте питание во время обновления BIOS, чтобы избежать возможных проблем.

Содержание

- Что такое микрокод процессора

- Шаг 1 — Подготовка к добавлению микрокода

- Проверка совместимости процессора и BIOS

Что такое микрокод процессора

Микрокод является частью биоса (Basic Input/Output System) – небольшой программы, размещенной на системной плате компьютера, которая запускается при включении питания и контролирует начальную загрузку операционной системы. Перед загрузкой ОС, биос инициализирует аппаратное обеспечение и выполняет другие задачи для подготовки системы к работе.

Микрокод процессора позволяет управлять и настраивать работу самого процессора, оптимизировать его функционирование и добавлять новые возможности без необходимости изменения аппаратной части. Это позволяет производителям выпускать обновления микрокода, чтобы исправить ошибки, улучшить производительность или добавить новые функции процессора.

Микрокод может быть обновлен путем программирования биоса. Для этого необходимо загрузить обновление микрокода на флеш-накопитель, затем запустить процесс обновления в программе управления биосом. В процессе обновления микрокода процессора необходимо быть осторожным и следовать инструкциям производителя, чтобы избежать возможных ошибок или повреждения процессора.

Микрокод процессора является важным компонентом, который обеспечивает правильную работу процессора и его совместимость с операционной системой. Установка обновления микрокода процессора может значительно повысить производительность и стабильность работы компьютера, поэтому регулярное обновление микрокода является рекомендуемой практикой для всех пользователей.

Шаг 1 — Подготовка к добавлению микрокода

Перед тем, как начать процедуру добавления микрокода процессора в BIOS, необходимо выполнить ряд подготовительных действий. Эти шаги помогут обеспечить безопасность и гарантировать успешное выполнение процедуры:

- Сделайте полную резервную копию данных, хранящихся на компьютере. Это позволит избежать потери информации в случае неудачного обновления BIOS.

- Удостоверьтесь, что на компьютере установлена последняя версия BIOS. Если нет, загрузите и установите обновление BIOS с официального сайта производителя материнской платы.

- Загрузите необходимый микрокод процессора с официального сайта производителя процессора. Обратите внимание на правильную модель процессора и версию BIOS.

- Запустите программу для обновления BIOS, предоставленную производителем материнской платы. Убедитесь, что выбрано «обновление микрокода процессора» или что аналогичная опция включена в процесс обновления BIOS.

После выполнения данных шагов вы будете готовы приступить к добавлению микрокода процессора в BIOS. Прежде чем продолжить, убедитесь, что все необходимые файлы загружены и резервная копия данных находится в безопасном месте.

Проверка совместимости процессора и BIOS

При добавлении микрокода процессора в BIOS необходимо убедиться в совместимости процессора с материнской платой и версией BIOS. Это важный шаг, который позволяет избежать проблем в работе системы и улучшить ее производительность.

Для проверки совместимости необходимо выполнить следующие действия:

- Определите модель и версию вашей материнской платы. Обычно эта информация указана на самой плате или в документации к ней.

- Определите модель и версию вашего процессора. Эту информацию можно найти на коробке процессора или в его технической спецификации.

- Посетите официальный сайт производителя материнской платы и найдите раздел поддержки или загрузок. Введите там модель и версию материнской платы.

- Найдите раздел с загрузками BIOS и найдите свою модель платы в списке поддерживаемых моделей.

- Сравните версию BIOS с текущей версией на вашей материнской плате. Если в новой версии BIOS есть добавленная поддержка вашего процессора, то они совместимы.

- Если после проверки выяснилось, что процессор и BIOS не совместимы, следует обратиться к производителю платы или найти альтернативные способы добавления микрокода процессора.

Проверка совместимости процессора и BIOS является важным шагом перед добавлением микрокода процессора. Это поможет избежать проблем с работой системы и обеспечить ее стабильность и производительность.

Эмуляция неподдерживаемого набора инструкций

| Автор | Сообщение | ||

|---|---|---|---|

|

|||

|

Junior Статус: Не в сети |

Для проги нужна поддержка SSE(или SSE2), а проц не поддерживает. Можно ли как нибудь сэмулировать ее, например ловить исключение «неизвестная инструкция», смотреть что там за инструкция и если это SSE инструкция эмулировать ее? В исключениях процессора не шарю, есть ли такое исключение вообще? |

| Реклама | |

|

Партнер |

|

Megagad |

|

|

Member Статус: Не в сети |

The Lich В ПОИСК! А по проблеме — НЕТ, нельзя эмулирвать то, что считается на аппаратном уровне в процессоре(особенно ССЕ1 и ССЕ2 |

|

The Lich |

|

|

Junior Статус: Не в сети |

Увы, в поиске не нашел ничего кроме полной эмуляции процессора. А аппаратная поддержка эмуляции может быть вполне, вот я хочу это выяснить. |

|

The Lich |

|

|

Junior Статус: Не в сети |

а можете объяснить, почему? был бы признателен |

|

Intelator |

|

|

Member Статус: Не в сети |

Простите за глупость Последний раз редактировалось Intelator 24.05.2009 9:00, всего редактировалось 1 раз. |

|

JohnGalt |

|

|

Junior Статус: Не в сети |

А почему нет? Только скорость обработки и возможно качество будут не очень |

|

Intelator |

|

|

Member Статус: Не в сети |

Простите за глупость Последний раз редактировалось Intelator 24.05.2009 9:00, всего редактировалось 1 раз. |

|

The Lich |

|

|

Junior Статус: Не в сети |

а можно без аналогий? проц i386 обладает довольно большими возможностями. |

|

Intelator |

|

|

Member Статус: Не в сети |

Он не знает, что делать. Чтобы это исправить, надо переписывать программу |

|

The Lich |

|

|

Junior Статус: Не в сети |

нет, он, по-моему, знает что делать. он вызывает соответствующее прерывание. но вот тут мои познания кончаются. какое прерывание он вызывает? можно ли после него продолжить работу? можно ли промотать IP на нужное число байтов? |

|

Megagad |

|

|

Member Статус: Не в сети |

The Lich писал(а): нет, он, по-моему, знает что делать. он вызывает соответствующее прерывание Как он может вызвать то, о чём не знает? Вообщето, если аппаратная часть не подходит под программу она вообще не запускается!!! Ну или выдаёт ошибку. Третьего не дано! |

|

The Lich |

|

|

Junior Статус: Не в сети |

вы хорошо разбираетесь в механизме прерываний i386? если нет, тогда, пожалуйста не отвечайте |

|

Megagad |

|

|

Member Статус: Не в сети |

The Lich Вообщето, прерывания тут непричём! А ССЕ и ССЕ2 это КОМАНДЫ!(инструкции) И если процессор не может их обработать — он НИЧЕГО не может с ними сделать. Вобщем изучайте: http://ru.wikipedia.org/wiki/SSE Ну и чисто, к слову, чтоб знать ССЕ проц должен как минимум знать ММХ: http://ru.wikipedia.org/wiki/MMX — чего за 386 я не замечал http://ru.wikipedia.org/wiki/I386 — изучайте |

|

The Lich |

|

|

Junior Статус: Не в сети |

Конечно, похоже что так делать нельзя, иначе у людей не было бы таких проблем, и были бы ссылки на эмули.

Я знаю, что такое MMX (что такое SSE не знаю, но догадываюсь что это).

только, наверное, при неизвестной инструкции он вызывает не специальное прерывание, а какое-нибудь общее «ошибка продолжение невозможно»

Я знаю, что такое MMX (что такое SSE не знаю, но догадываюсь что это). только, наверное, при неизвестной инструкции он вызывает не специальное прерывание, а какое-нибудь общее «ошибка продолжение невозможно»

ничего читать сейчас не имею возможности, иначе обязательно бы прочитал |

|

HertZ |

|

|

Advanced member Статус: Не в сети |

The Lich писал(а): А если можно, есть ли такие эмуляторы? Универсальных готовых решений нет, но можно эмулировать процессор целиком: http://bochs.sourceforge.net/getcurrent.html The Lich писал(а): вот он натыкается на неизвестную инструкцию. что дальше происходит? Генерится исключение, и его можно перехватить. The Lich писал(а): Можно ли как нибудь сэмулировать ее, например ловить исключение «неизвестная инструкция», смотреть что там за инструкция и если это SSE инструкция эмулировать ее? Можно, но отлов исключений по каждому вызову чреват большими тормозами. Megagad писал(а): А по проблеме — НЕТ, нельзя эмулирвать то, что считается на аппаратном уровне в процессоре(особенно ССЕ1 и ССЕ2 Sad ). Можно, просто никто этим не занимается. Intelator писал(а): Как думаете, на калькуляторе можно эмулировать обработку графики, например? Intelator писал(а): Тогда дугой пример Smile Можно на лопате эмулировать вертолет? Когда тупишь, добавляй «имхо». А вообще, советую не тупить. Особенно, если ничего не можешь сказать по теме. http://www.cracklab.ru/f/index.php?acti … =6&page=-1 Поговори с автором этой темы, может он чего путного тебе подскажет. Кстати, пример перехватчика там тоже есть, правда малость недоделанный. |

|

The Lich |

|

|

Junior Статус: Не в сети |

спасибо за ссылку. |

|

HertZ |

|

|

Advanced member Статус: Не в сети |

The Lich Цитата: 95% SSE кода это:

Ну действительно, без ссе просто никак В общем, проще всего вопрос решить можно переделкой JIT, разработанного ntldr, под эти нужды. Производительность в целом несколько пострадает, зато можно будет избежать накладных расходов и геморроя при отлове исключений.. Более универсальное решение, что-ли.. |

|

Megagad |

|

|

Member Статус: Не в сети |

HertZ писал(а): Можно, просто никто этим не занимается. Эм, тода мине пожалуйста эмулятор ССЕ2 для бартона, пару штучек |

|

HertZ |

|

|

Advanced member Статус: Не в сети |

Megagad, берите исходники из топика по ссылке выше, и дописывайте Мне, если честно, не очень хочется этим заниматься… Разве что за денежку.. |

—

Кто сейчас на конференции |

|

Сейчас этот форум просматривают: нет зарегистрированных пользователей и гости: 1 |

| Вы не можете начинать темы Вы не можете отвечать на сообщения Вы не можете редактировать свои сообщения Вы не можете удалять свои сообщения Вы не можете добавлять вложения |